#### Copyright

This documentation and the software included with this product are copyrighted 2002 by Advantech Co., Ltd. All rights are reserved. Advantech Co., Ltd. reserves the right to make improvements in the products described in this manual at any time without notice. No part of this manual may be reproduced, copied, translated or transmitted in any form or by any means without the prior written permission of Advantech Co., Ltd. Information provided in this manual is intended to be accurate and reliable. However, Advantech Co., Ltd. assumes no responsibility for its use, nor for any infringements of the rights of third parties which may result from its use.

#### **Acknowledgments**

PC-LabCard is a trademark of Advantech Co., Ltd. IBM and PC are trademarks of International Business Machines Corporation. MS-DOS, Windows, Microsoft Visual C++ and Visual BASIC are trademarks of Microsoft Corporation. Intel and Pentium are trademarks of Intel Corporation. Delphi and C++ Builder are trademarks of Inprise Corporation.

#### **CE** notification

The PCI-1784, developed by ADVANTECH CO., LTD., has passed the CE test for environmental specifications when shielded cables are used for external wiring. We recommend the use of shielded cables. This kind of cable is available from Advantech. Please contact your local supplier for ordering information.

#### **On-line Technical Support**

For technical support and service, please visit our support website at: http://www.advantech.com/support

#### Note:

Note Concerning the environment protection, we'd like to reduce the paper using for the user's manual. Starting the page of *Appendix C*, please find the PDF file of the CD-ROM.

Part No. 2003178400 1st Edition Printed in Taiwan July 2002

# **Contents**

| 1. INT  | RODUCTION                                        | 1  |

|---------|--------------------------------------------------|----|

| 1.1     | FEATURES                                         | 1  |

| 1.2     | APPLICATIONS                                     | 4  |

| 1.3     | INSTALLATION GUIDE                               | 4  |

| 1.4     | SOFTWARE OVERVIEW                                | 6  |

| 1.5     | DEVICE DRIVERS PROGRAMMING ROADMAP               | 7  |

| 1.6     | Accessories                                      | 9  |

| 2. INS  | TALLATION                                        | 10 |

| 2.1     | Unpacking                                        | 10 |

| 2.2     | DRIVER INSTALLATION                              | 12 |

| 2.3     | HARDWARE INSTALLATION                            | 13 |

| 2.4     | DEVICE SETUP & CONFIGURATION                     | 16 |

| 3. SIG  | NAL CONNECTIONS                                  | 19 |

| 3.1     | Overview                                         | 19 |

| 3.2     | SWITCH AND JUMPER SETTINGS                       | 19 |

| 3.3     | SIGNAL CONNECTIONS                               | 21 |

| APPE    | NDIX A. SPECIFICATIONS                           | 25 |

| APPE    | NDIX B. BLOCK DIAGRAM                            | 27 |

| APPE    | NDIX C. REGISTER STRUCTURE AND FORMAT            | 29 |

| C.1     | Overview                                         | 29 |

| C.2     | I/O PORT ADDRESS MAP                             | 29 |

| C.3     | COUNTER 0/1/2/3 MODE — BASE+00/04/08/0CH         | 33 |

| C.4     | COUNTER 0/1/2/3 LATCH DATA — BASE+00/04/08/0CH   | 35 |

| C.5     | COUNTER 0/1/2/3 COMPARE DATA — BASE+10/14/18/1CH | 36 |

| C.6     | INTERRUPT CONTROL REGISTER — BASE+20H            | 37 |

| C.7     | INTERRUPT STATUS REGISTER — BASE+20H             | 38 |

| C.8     | CLEAR INTERRUPT — BASE+24H                       | 39 |

| $C_{9}$ | CLEAR INTERRUPT RASE+24H                         | 40 |

| C.10  | SOFTWARE LATCH — BASE+28H       | 41 |

|-------|---------------------------------|----|

| C.11  | BOARD ID — BASE+28H             | 42 |

| C.12  | RESET COUNTER — BASE+2CH        | 43 |

| C.13  | DIGITAL OUTPUT — BASE+30H       | 44 |

| C.14  | DIGITAL INPUT/OUTPUT — BASE+30H | 45 |

| APPEN | DIX D. OPERATION                | 47 |

| D.1   | QUADRATURE ENCODER INTRODUCTION | 47 |

| D.2   | COUNTER MODES                   | 48 |

| D.3   | DIGITAL NOISE FILTER            | 49 |

| D.4   | LATCH MODE                      | 50 |

| D.5   | COUNTER RESET VALUE             | 51 |

| D.6   | TIMER FUNCTION                  | 51 |

| D.7   | Interrupt function              | 52 |

### 1. Introduction

Thank you for buying the Advantech PCI-1784. The PCI-1784 is a 4-axis quadrature encoder and counter card for PCI bus. This card includes four 32-bit quadruple AB phase encoder counters, 8-bit timer with multi range time-base selector and four isolated digital input and four isolated digital output. Its flexible interrupt sources are suitable for motor control and position monitoring.

The following sections of this chapter will provide further information about features of the multifunction cards, a Quick Start for installation, together with some brief information on software and accessories for the PCI-1784 card.

#### 1.1 Features

| ☐ Four 32-bit up/down counters                                 |

|----------------------------------------------------------------|

| ☐ Single ended or differential inputs                          |

| ☐ Pulse/direction and up/down counter                          |

| □ x1, x2, x4 counts for each encoder cycle                     |

| $\Box$ Optically isolated up to 2500 $V_{DC}$                  |

| ☐ 4-stage digital filter with selectable sampling rate         |

| $\Box$ On board 8-bit timer with wide range time-base selector |

| ☐ Multiple interrupt sources for precision application         |

| ☐ Four isolated digital input                                  |

| ☐ Four isolated digital output with flexible function          |

| □ Board ID                                                     |

The Advantech PCI-1784 offers the following main features:

#### **Encoder Interface**

Each channel includes a decoding circuit for incremental quadrature encoding. Inputs accept either single-ended or differential signals. Quadrature input works with or without an index, allowing linear or rotary encoder feedback.

#### Counters

The PCI-1784 has four independent 32-bit counters. The maximum quadrature input rate is 2 MHz, and the maximum input rate in counter mode is 8 MHz. You can individually configure each counter for quadrature decoding, pulse/direction counting or up/down counting.

#### **Digital Input and Interrupts**

The PCI-1784 provides four digital input channels. Each channel accepts digital input as an index input for a rotary encoder or as a home sensor input for a linear encoder. The card can generate an interrupt to the system based on a signal from its digital inputs, overflow/underflow and over-compare/under-compare of its counters, or on a programmed time interval. It can repeatedly generate interrupts at any time interval you specify, from 20 micro second to 51 second. These interrupts let you precisely monitor the speed of a control system.

#### **Flexible Digital Output function**

The PCI-1784 provides four digital output channels. Each channel accepts digital output as a normal TTL output for a rotary encoder, or as an indicated output with pulse/level mode for a linear encoder. The PCI-1784 can generate an indicated output based on a signal from over-compare/under-compare of its counters. The pulse width of an indicated output is depends on the counter clock or clear interrupt.

#### Special Shielded Cable for Noise Reduction

The PCL-10137H shielded cable is specially designed for the PCI-1784 for reducing noise. Its wires are all twisted pairs, and the input signals and output signals are separately shielded, providing minimal cross talk between signals and the best protection against EMI/EMC problems.

## Keeping the Counter Values and the Output Status after system reset

Users can independently use the four counter channels. When the system is hot reset (power not shut down), the PCI-1784 can either retain the last counter values and the output status, or return to its

default configuration, depending on jumper setting. This practical function eliminates danger caused by miss-operation during unexpected system reset.

#### **Board ID**

The PCI-1784 has a built-in DIP Switch that helps define each card's ID when multiple PCI-1784 cards have been installed on the same PC chassis. The board ID setting function is very useful when users build their system with multiple PCI-1784 cards. With correct Board ID settings, you can easily identify and access each card during hardware configuration and software programming.

#### Note:

➤ For detailed specifications of the PCI-1784, please refer to *Appendix A*, *Specifications*.

| 1.2 | Applications                                                         |                                          |  |  |  |

|-----|----------------------------------------------------------------------|------------------------------------------|--|--|--|

|     | ☐ Motion control                                                     |                                          |  |  |  |

|     | ☐ Position sensing, monit                                            | oring and measuring                      |  |  |  |

|     | ☐ Coordinate measuring i                                             | machines                                 |  |  |  |

|     | □ X-Y table monitors                                                 |                                          |  |  |  |

|     | □ Robotics                                                           |                                          |  |  |  |

|     | ☐ Machine control                                                    |                                          |  |  |  |

| 1.3 | Installation Guide                                                   |                                          |  |  |  |

|     | Before you install your PCI-1784 card, please make sure you have the |                                          |  |  |  |

|     | following necessary components:                                      |                                          |  |  |  |

|     | □ PCI-1784 DA&C card                                                 | I                                        |  |  |  |

|     | □ PCI-1784 User's Man                                                | ual                                      |  |  |  |

|     | ☐ Driver software                                                    | Advantech DLL drivers                    |  |  |  |

|     |                                                                      | (included in the companion CD-ROM)       |  |  |  |

|     | ☐ Wiring cable                                                       | PCL-10137H (option)                      |  |  |  |

|     | ☐ Wiring board                                                       | ADAM-3937 (option)                       |  |  |  |

|     | □ Computer                                                           | Personal computer or workstation with a  |  |  |  |

|     |                                                                      | PCI-bus slot (running Windows 2000/95/98 |  |  |  |

|     |                                                                      | NT/ME/XP)                                |  |  |  |

|     | Some other optional componention:                                    | ponents are also available for enhanced  |  |  |  |

|     | ☐ Application software                                               | ActiveDAQ, GeniDAQ or other third-party  |  |  |  |

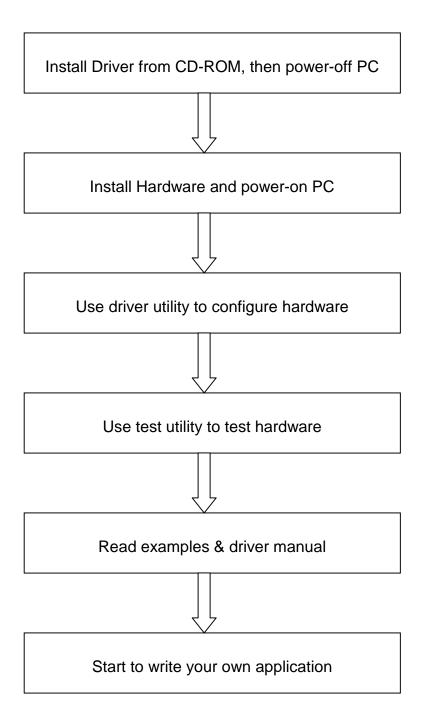

After you get the necessary components and maybe some of the accessories for enhanced operation of your Multifunction card, you can then begin the Installation procedures. Figure 1-1 on the next page provides a concise flow chart to give users a broad picture of the software and hardware installation procedures:

software packages

Fig. 1-1 Installation Flow Chart

#### 1.4 Software Overview

Advantech offers a rich set of DLL drivers, third-party driver support and application software to help fully exploit the functions of your PCI-1784 card:

|   | Device Drivers (on the companion CD-ROM) |

|---|------------------------------------------|

|   | LabVIEW driver*                          |

|   | Advantech ActiveDAQ                      |

| _ | Advantech GeniDAQ                        |

Programming choices for DA&C cards: You may use Advantech application software such as Advantech Device Drivers. On the other hand, advanced users are allowed another option for register-level programming, although not recommended due to its laborious and time-consuming nature.

#### **Device Drivers**

The Advantech Device Drivers software is included on the companion CD-ROM at no extra charge. It also comes with all the Advantech DA&C cards. Advantech's device drivers features a complete I/O function library to help boost your application performance. The Advantech Device Drivers for Windows 2000/95/98/ ME/NT/XP works seamlessly with development tools such as Visual C++, Visual Basic, Inprise C++ Builder and Inprise Delphi.

#### **Register-level Programming**

Register-level programming is reserved for experienced programmers who find it necessary to write codes directly at the level of device registers. Since register-level programming requires much effort and time, we recommend that you use the Advantech Device Drivers instead. However, if register-level programming is indispensable, you should refer to the relevant information in *Appendix C, Register Structure and Format*, or to the example codes included on the companion CD-ROM.

### 1.5 Device Drivers Programming Roadmap

This section will provide you a roadmap to demonstrate how to build an application from scratch using Advantech Device Drivers with your favorite development tools such as Visual C++, Visual Basic, Delphi and C++ Builder. The step-by-step instructions on how to build your own applications using each development tool will be given in the *Device Drivers Manual*. Moreover, a rich set of example source codes are also given for your reference.

#### **Programming Tools**

□ C++ Builder

| Programmers can develop application programs with their favorite |

|------------------------------------------------------------------|

| development tools:                                               |

| □ Visual C++                                                     |

| □ Visual Basic                                                   |

| □ Delphi                                                         |

For instructions on how to begin programming works in each development tool, Advantech offers a *Tutorial* Chapter in the *Device Drivers Manual* for your reference. Please refer to the corresponding sections in this chapter on the *Device Drivers Manual* to begin your programming efforts. You can also take a look at the example source codes provided for each programming tool, since they can get you very well-oriented.

The *Device Drivers Manual* can be found on the companion CD-ROM. Or if you have already installed the Device Drivers on your system, The *Device Drivers Manual* can be readily accessed through the *Start* button:

#### Start/Programs/Advantech Driver V2.0/Device Driver Manual

The example source codes could be found under the corresponding installation folder such as the default installation path:

\Program Files\Advantech\ADSAPI\Examples

For information about using other function groups or other development tools, please refer to the *Creating Windows 95/NT/2000 Application with Device Drivers* chapter and the *Function Overview* chapter on the *Device Drivers Manual*.

#### **Programming with Device Drivers Function Library**

Advantech Device Drivers offers a rich function library to be utilized in various application programs. This function library consists of numerous APIs that support many development tools, such as Visual C++, Visual Basic, Delphi and C++ Builder.

According to their specific functions or services, those APIs can be categorized into several function groups:

- □ Digital Input/Output Function Group

- **□** Counter Function Group

- □ Port Function Group (direct I/O)

- **□** Event Function Group

For the usage and parameters of each function, please refer to the *Function Overview* chapter in the *Device Drivers Manual*.

#### **Troubleshooting Device Drivers Error**

Driver functions will return a status code when they are called to perform a certain task for the application. When a function returns a code that is not zero, it means the function has failed to perform its designated function. To troubleshoot the Device Drivers error, you can pass the error code to **DRV\_GetErrorMessage** function to return the error message. Or you can refer to the *Device Drivers Error Codes* Appendix in the *Device Drivers Manaul* for a detailed listing of the Error Code, Error ID and the Error Message.

#### 1.6 Accessories

Advantech offers a complete set of accessory products to support the PCI-1784 card. These accessories include:

#### Wiring Cable

□ PCL-10137H The PCL-10137H shielded cable is specially designed for PCI-1784 cards to provide high resistance to noise.

To achieve a better signal quality, the signal wires are twisted in such a way as to form a "twisted-pair cable", reducing cross-talk and noise from other signal sources. Furthermore, its analog and digital lines are separately sheathed and shielded to neutralize EMI/EMC problems.

#### **Wiring Boards**

□ ADAM-3937 The ADAM-3937 is a 37-pin D-type wiring terminal module for DIN-rail mounting. This terminal module can be readily connected to the Advantech PC-Lab cards and allow easy yet reliable access to individual

pin connections for the PCI-1784 card.

## 2. Installation

This chapter gives users a package item checklist, proper instructions about unpacking and step-by-step procedures for both driver and card installation.

## 2.1 Unpacking

After receiving your PCI-1784 package, please inspect its contents first. The package should contain the following items:

- ☑ PCI-1784 card

- ☑ Companion CD-ROM (DLL driver included)

- ☑ User's Manual

The PCI-1784 card harbors certain electronic components vulnerable to *electrostatic discharge* (ESD). ESD could easily damage the integrated circuits and certain components if preventive measures are not carefully paid attention to.

# Before removing the card from the antistatic plastic bag, you should take following precautions to ward off possible ESD damage:

- Touch the metal part of your computer chassis with your hand to discharge static electricity accumulated on your body. Or one can also use a grounding strap.

- Touch the anti-static bag to a metal part of your computer chassis before opening the bag.

- Take hold of the card only by the metal bracket when removing it out of the bag.

#### After taking out the card, first you should:

• Inspect the card for any possible signs of external damage (loose or damaged components, etc.). If the card is visibly damaged, please notify our service department or our local sales representative immediately. Avoid installing a damaged card into your system.

# Also pay extra caution to the following aspects to ensure proper installation:

- Avoid physical contact with materials that could hold static electricity such as plastic, vinyl and Styrofoam.

- ✓ Whenever you handle the card, grasp it only by its edges. DO NOT TOUCH the exposed metal pins of the connector or the electronic components.

#### Note:

★ Keep the anti-static bag for future use. You might need the original bag to store the card if you have to remove the card from PC or transport it elsewhere.

#### 2.2 Driver Installation

We recommend you to install the driver before you install the PCI-1784 card into your system, since this will guarantee a smooth installation process.

The Advantech Device Drivers Setup program for the PCI-1784 card is included on the companion CD-ROM that is shipped with your DA&C card package. Please follow the steps below to install the driver software:

**Step 1:** Insert the companion CD-ROM into your CD-ROM drive.

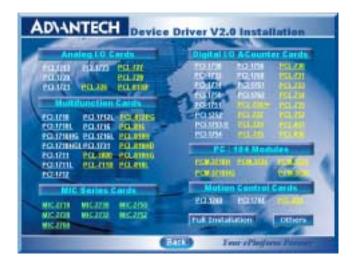

**Step 2:** The Setup program will be launched automatically if you have the autoplay function enabled on your system. When the Setup Program is launched, you'll see the following Setup Screen.

#### Note:

■ If the autoplay function is not enabled on your computer, use Windows Explorer or Windows *Run* command to execute SETUP.EXE on the companion CD-ROM.

Fig. 2-1 The Setup Screen of Advantech Automation Software

- **Step 3:** Select the *Individual Drivers* option.

- **Step 4:** Select the specific device then just follow the installation instructions step by step to complete your device driver setup.

Fig. 2-2 Different options for Driver Setup

For further information on driver-related issues, an online version of *Device Drivers Manual* is available by accessing the following path:

Start/Programs/Advantech Device Drivers V2.0/Device Driver Manual

#### 2.3 Hardware Installation

#### Note:

Make sure you have installed the driver first before you install the card

(please refer to 2.2 Driver Installation)

After the DLL driver installation is completed, you can now go on to install the PCI-1784 card in any PCI slot on your computer. But it is suggested that you should refer to the computer user manual or related documentation if you have any doubt. Please follow the steps below to install the card on your system.

- **Step 1:** Turn off your computer and unplug the power cord and cables. TURN OFF your computer before installing or removing any components on the computer.

- **Step 2:** Remove the cover of your computer.

- **Step 3:** Remove the slot cover on the back panel of your computer.

- **Step 4:** Touch the metal part on the surface of your computer to neutralize the static electricity that might be on your body.

- **Step 5:** Insert the PCI-1784 card into a PCI slot. Hold the card only by its edges and carefully align it with the slot. Insert the card firmly into place. Use of excessive force must be avoided, otherwise the card might be damaged.

- **Step 6:** Fasten the bracket of the PCI card on the back panel rail of the computer with screws.

- **Step 7:** Connect appropriate accessories (37-pin cable, wiring terminals, etc. if necessary) to the PCI card.

- **Step 8:** Replace the cover of your computer chassis. Re-connect the cables you removed in step 2.

- **Step 9:** Plug in the power cord and turn on the computer.

#### Note:

Note Note Note 1 Note 1 Note 1 Note 1 Note 2 Note

After the PCI-1784 card is installed, you can verify whether it is properly installed on your system in the *Device Manager*:

- 1. Access the *Device Manager* through *Control Panel/System/Device Manager*.

- 2. The *device name* of the PCI-1784 should be listed on the *Device Manager* tab on the System *Property* Page.

Fig. 2-3 The device name listed on the Device Manager

#### **Note:**

■ If your card is properly installed, you should see the device name of your card listed on the Device Manager tab. If you do see your device name listed on it but marked with an exclamation sign "!", it means your card has not been correctly installed. In this case, remove the card device from the Device Manager by selecting its device name and press the Remove button. Then go through the driver installation process again.

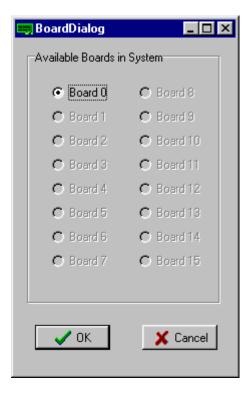

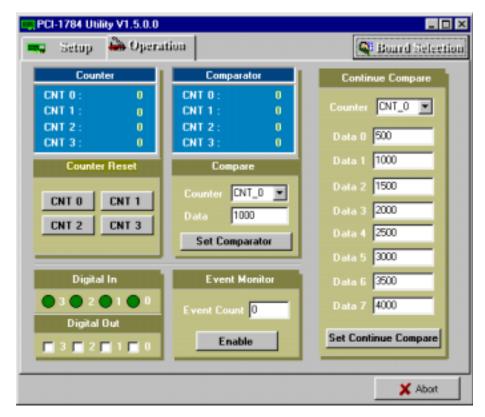

After your card is properly installed on your system, you can now configure your device using the *PCI-1784 Utility* program that has itself already been installed on your system during driver setup. A complete device installation procedure should include *board selection* and *device setup*. After that, you can operate this card through the *operation*. The following sections will guide you through the *board selection*, *device setup* and *operation* of your device.

## 2.4 Device Setup & Configuration

The *PCI-1784 Utility* program is a utility that allows you to setup, configure and test your device, and later stores your settings on the system registry. These settings will be used when you call the APIs of Advantech Device Drivers.

#### **Board selection**

After your card is properly inserted, the Windows system will install the drivers properly. You just need to launch the *PCI-1784 Utility* for board selection. Click *Board Selection* and the *board dialog* box will appear as seen below (Fig. 2-4):

Fig. 2-4 The 'Board Selection' dialog box

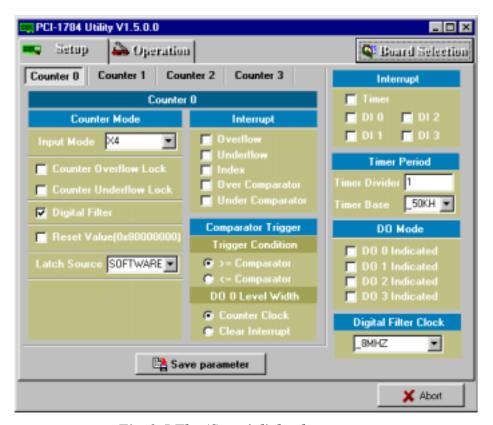

#### Setting Up and configure the device

Click *Setup* to configure each parameter. The dialog box will appear as seen below (Fig. 2-5):

Fig. 2-5 The 'Setup' dialog box

Fig. 2-6 The "Operation" dialog box

After your card is properly installed and configured, you can click the *Operation* button to test your hardware. For more detailed information, please refer to *Chapter 2* of the *Device Drivers Manual*.

You can also find the rich examples on the CD-ROM to speeding up your programming.

## 3. Signal Connections

## 3.1 Overview

Maintaining signal connections is one of the most important factors in ensuring that your application system is sending and receiving data correctly. A good signal connection can avoid unnecessary and costly damage to your PC and other hardware devices. This chapter provides useful information about how to connect input and output signals to the PCI-1784 via the I/O connector.

## 3.2 Switch and Jumper Settings

The PCI-1784 card has one function switch and five jumper settings.

Fig. 3-1 Card connector, jumper and switch locations

Table 3-1: Summary of jumper settings

| Names of Jumpers | Function description |                                  |  |

|------------------|----------------------|----------------------------------|--|

| JP2              | 0                    | Keep last status after hot reset |  |

| JP2              | 0                    | Default configuration            |  |

# Setting the time to reset the digital outputs and the counter value

Some users will want the capability of clearing each counter and the isolated digital output when the system (or PC) issues a reset signal on the PCI bus. Some users will want to clear their counter and digital output only as part of system power-on.

The PCI-1784 satisfies both these needs by providing jumper JP2. Depending on the application, this capability may allow counter value and the isolated digital outputs to be "OFF" without requiring a complete shutdown of processes controlled by the card.

Complete loss of power to the chip clears the chip memory. Thus, no matter how JP2 is set, if the power to the PCI-1784 is disconnected, the counter value and the isolated digital output initial power-on state will be "OFF".

## **Board ID setting (SW1)**

| ID3 | ID2 | ID1 | ID0 | <b>Board ID</b> |

|-----|-----|-----|-----|-----------------|

| 1   | 1   | 1   | 1   | 0               |

| 1   | 1   | 1   | 0   | 1               |

| 1   | 1   | 0   | 1   | 2               |

| 1   | 1   | 0   | 0   | 3               |

| 1   | 0   | 1   | 1   | 4               |

| 1   | 0   | 1   | 0   | 5               |

| 1   | 0   | 0   | 1   | 6               |

| 1   | 0   | 0   | 0   | 7               |

| 0   | 1   | 1   | 1   | 8               |

| 0   | 1   | 1   | 0   | 9               |

| 0   | 1   | 0   | 1   | 10              |

| 0   | 1   | 0   | 0   | 11              |

| 0   | 0   | 1   | 1   | 12              |

| 0   | 0   | 1   | 0   | 13              |

| 0   | 0   | 0   | 1   | 14              |

| 0   | 0   | 0   | 0   | 15              |

**Note:** On: 1, Off: 0

## 3.3 Signal Connections

## **Pin Assignment**

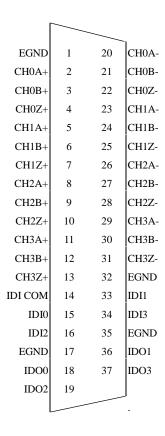

Figure 3-2 shows the pin assignments for the 37-pin I/O connector on the PCI-1784.

Fig. 3-2 I/O connector pin assignments for the PCI-1784

## I/O Connector Signal Description

Table 3-2 I/O Connector Signal Description

| Signal Name | Reference | Direction | Description                                    |  |

|-------------|-----------|-----------|------------------------------------------------|--|

| EGND        | -         | 1         | External Ground.                               |  |

| CH<03>A+    | EGND      | Input     | Channel <03> A differential positive-input.    |  |

| CH<03>A-    | EGND      | Input     | Channel <03> A differential negative-input.    |  |

| CH<03>B+    | EGND      | Input     | Channel <03> B differential positive-input.    |  |

| CH<03>B-    | EGND      | Input     | Channel <03> B differential negative-input.    |  |

| CH<03>Z+    | EGND      | Input     | Channel <03> Z differential positive-input.    |  |

| CH<03>Z-    | EGND      | Input     | Channel <03> Z differential negative-input.    |  |

| IDI<03>     | IDI COM   | Input     | Isolated Digital Input, Channels 0 through 3.  |  |

| IDI COM     | -         | -         | Common input of the Isolated Digital Input.    |  |

| IDO<03>     | EGND      | Output    | Isolated Digital Output, Channels 0 through 3. |  |

| EGND        | -         | -         | External Ground.                               |  |

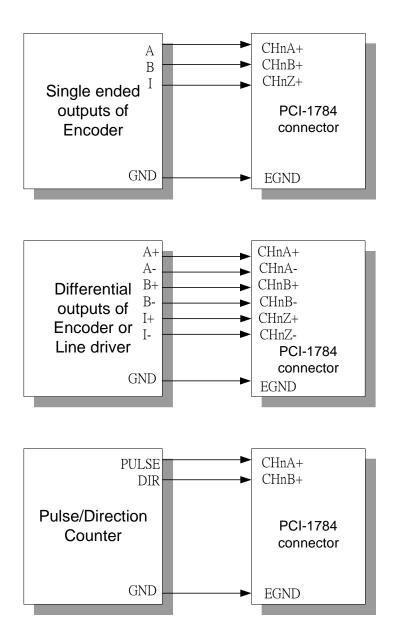

## **Quadrature encoder input**

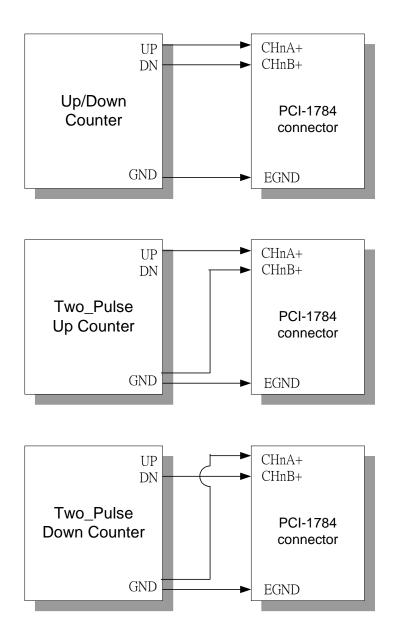

Figure 3-3: Quadrature encoder input connections

Figure 3-4: Quadrature encoder (up/down counter) input connections

#### **Note:**

No In case you want to connect the Up/Down counter signal into the PCI-1784, be sure that all the signals must be connected. The floating connection will cause unexpected result.

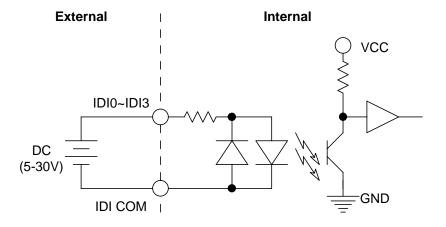

## Isolated digital input

Figure 3-4: Isolated digital input connections

## Isolated digital output

Figure 3-5: Isolated digital output connections

## **Appendix A. Specifications**

## **Encoder Output**

| Number of Axis                | 4 (independent)                      |         |  |

|-------------------------------|--------------------------------------|---------|--|

| Resolution                    | 32-bit                               |         |  |

| Max. Quadrature               | w/ Digital Filter                    | 1.0 MHz |  |

| Input Frequency               | w/o Digital<br>Filter                | 2.0 MHz |  |

| Digital Filter                | 4 stage                              |         |  |

| Drive Type                    | Single-ended or differential         |         |  |

| Counter Mode                  | Quadrature, Up/Down, Count/Direction |         |  |

| Optical Isolation             | 2500 V <sub>DC</sub>                 |         |  |

| Max. Input Pulse<br>Frequency | x 1, x 2, x 4                        |         |  |

| Sample Clock<br>Frequency     | 8, 4, 2, or 1 MHz                    |         |  |

## Timer

| Resolution | 8-bit                    |  |

|------------|--------------------------|--|

| Time base  | 50 K, 5 K, 500, 50, 5 Hz |  |

## **Isolated Digital Input**

| Number of Channel           | 4                    |                    |  |

|-----------------------------|----------------------|--------------------|--|

| Optical Isolation           | 2500 V <sub>DC</sub> |                    |  |

| Opto-isolator response time | 25μs                 |                    |  |

| Over-voltage Protect        |                      | 70 V <sub>DC</sub> |  |

|                             | VIH (max.)           | $30 V_{DC}$        |  |

| Input Voltage               | VIH (min.)           | 10 V <sub>DC</sub> |  |

|                             | VIL (max.)           | $3 V_{DC}$         |  |

|                             | 10 V <sub>DC</sub>   | 1.7 mA (typical)   |  |

| Input Current               | $12 V_{DC}$          | 2.1 mA (typical)   |  |

|                             | $24 V_{DC}$          | 4.4 mA (typical)   |  |

## **Isolated Digital Output**

| Number of Channel   | 4                    |

|---------------------|----------------------|

| Optical Isolation   | 2500 V <sub>DC</sub> |

| Response time       | 20 μs (max.)         |

| Supply Voltage      | TTL level            |

| Sink/Source Current | 50 mA max./channel   |

## Interrupt

| Source | Counter overflow, Counter underflow,       |

|--------|--------------------------------------------|

| Source | Index input, Compare, Timer, Digital input |

## **Counter Latch**

| Source | Software, Timer, Index input, Digital input |

|--------|---------------------------------------------|

## General

| I/O Connector Type | 37-pin D-sub female                             |                                              |  |  |  |  |  |

|--------------------|-------------------------------------------------|----------------------------------------------|--|--|--|--|--|

| Dimensions         | 175 mm x 100 mm (6.9" x 3.9")                   |                                              |  |  |  |  |  |

| Power Consumption  | Typical                                         | +5 V @ 200 mA                                |  |  |  |  |  |

| 1 ower consumption | Max.                                            | +5 V @ 450 mA                                |  |  |  |  |  |

| Temperature        | Operation                                       | 0~60°C (32~140°F)<br>(refer to IEC 68-2-1,2) |  |  |  |  |  |

| ·                  | Storage                                         | -20~70°C (-4~158°F)                          |  |  |  |  |  |

| Relative Humidity  | 5~95%RH non-condensing<br>(refer to IEC 68-2-3) |                                              |  |  |  |  |  |

| Certification      | CE certified                                    |                                              |  |  |  |  |  |

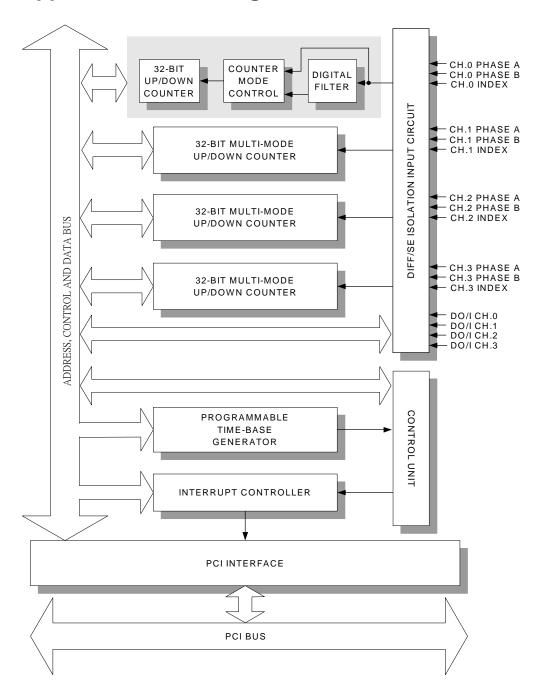

## Appendix B. Block Diagram

## **Appendix C. Register Structure and Format**

## C.1 Overview

The PCI-1784 is delivered with an easy-to-use 32-bit DLL driver for user programming under the Windows 2000/95/98/NT/ME/XP operating system. We advise users to program the PCI-1784 using the 32-bit DLL driver provided by Advantech to avoid the complexity of low-level programming by register.

The most important consideration in programming the PCI-1784 the register level is to understand the function of the card's registers. The information in the following sections is provided only for users who would like to do their own low-level programming.

## C.2 I/O Port Address Map

The PCI-1784 requires 32 consecutive addresses in the PC's I/O space. The address of each register is specified as an offset from the card's base address. For example, BASE+0 is the card's base address and BASE+6 is the base address plus six bytes.

The table C-1 shows the function of each register of the PCI-1784 or driver and its address relative to the card's base address.

Table C-1 PCI-1784 register format (Part 1)

| Ba    | Base |                      |                |     |     |     |     | PCI-17 | '84 Re | gister l | Forma | t   |     |     |     |     |     |

|-------|------|----------------------|----------------|-----|-----|-----|-----|--------|--------|----------|-------|-----|-----|-----|-----|-----|-----|

| Addı  |      | 15                   | 14             | 13  | 12  | 11  | 10  | 9      | 8      | 7        | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

| + HEX |      | 31                   | 30             | 29  | 28  | 27  | 26  | 25     | 24     | 23       | 22    | 21  | 20  | 19  | 18  | 17  | 16  |

|       |      | Counter 0 Mode       |                |     |     |     |     |        |        |          |       |     |     |     |     |     |     |

|       | W    | DI3                  | DI2            | DI1 | DI0 |     | TM  | IX     | SW     | DF       | UL    | OL  | RF  |     | M2  | M1  | МО  |

| 00H   |      |                      |                |     |     |     |     |        |        |          |       |     |     |     |     |     |     |

| 0011  |      | Counter 0 Latch Data |                |     |     |     |     |        |        |          |       |     |     |     |     |     |     |

|       | R    | D15                  | D14            | D13 | D12 | D11 | D10 | D9     | D8     | D7       | D6    | D5  | D4  | D3  | D2  | D1  | D0  |

|       |      | D31                  | D30            | D29 | D28 | D27 | D26 | D25    | D24    | D23      | D22   | D21 | D20 | D19 | D18 | D17 | D16 |

|       |      |                      | Counter 1 Mode |     |     |     |     |        |        |          |       |     |     |     |     |     |     |

|       | W    | DI3                  | DI2            | DI1 | DI0 |     | TM  | IX     | SW     | DF       | UL    | OL  | RF  |     | M2  | M1  | MO  |

| 04H   |      |                      |                |     |     |     |     |        |        |          |       |     |     |     |     |     |     |

| 0     | R    |                      |                |     |     |     |     | Cou    | nter 1 | Latch    | Data  |     |     |     |     |     |     |

|       |      | D15                  | D14            | D13 | D12 | D11 | D10 | D9     | D8     | D7       | D6    | D5  | D4  | D3  | D2  | D1  | D0  |

|       |      | D31                  | D30            | D29 | D28 | D27 | D26 | D25    | D24    | D23      | D22   | D21 | D20 | D19 | D18 | D17 | D16 |

|       |      |                      | Counter 2 Mode |     |     |     |     |        |        |          |       |     |     |     |     |     |     |

|       | W    | DI3                  | DI2            | DI1 | DI0 |     | TM  | IX     | SW     | DF       | UL    | OL  | RF  |     | M2  | M1  | MO  |

| 08H   |      |                      |                |     |     |     |     |        |        |          |       |     |     |     |     |     |     |

| 0011  |      | Counter 2 Latch Data |                |     |     |     |     |        |        |          |       |     |     |     |     |     |     |

|       | R    | D15                  | D14            | D13 | D12 | D11 | D10 | D9     | D8     | D7       | D6    | D5  | D4  | D3  | D2  | D1  | D0  |

|       |      | D31                  | D30            | D29 | D28 | D27 | D26 | D25    | D24    | D23      | D22   | D21 | D20 | D19 | D18 | D17 | D16 |

|       |      |                      | Counter 3 Mode |     |     |     |     |        |        |          |       |     |     |     |     |     |     |

|       | W    | DI3                  | DI2            | DI1 | DI0 |     | TM  | IX     | SW     | DF       | UL    | OL  | RF  |     | M2  | M1  | MO  |

| 0CH   |      |                      |                |     |     |     |     |        |        |          |       |     |     |     |     |     |     |

|       |      |                      |                |     |     |     |     | Cou    | nter 3 | Latch    | Data  |     |     |     |     |     |     |

|       | R    | D15                  | D14            | D13 | D12 | D11 | D10 | D9     | D8     | D7       | D6    | D5  | D4  | D3  | D2  | D1  | D0  |

|       |      | D31                  | D30            | D29 | D28 | D27 | D26 | D25    | D24    | D23      | D22   | D21 | D20 | D19 | D18 | D17 | D16 |

Table C-1 PCI-1784 register format (Part 2)

| Ba    | se |     |                        |     |     |     |     | PCI-17 | 784 Re  | gister l | Forma  | t   |     |     |     |     |     |

|-------|----|-----|------------------------|-----|-----|-----|-----|--------|---------|----------|--------|-----|-----|-----|-----|-----|-----|

| Addı  |    | 15  | 14                     | 13  | 12  | 11  | 10  | 9      | 8       | 7        | 6      | 5   | 4   | 3   | 2   | 1   | 0   |

| + HE  | ΕX | 31  | 30                     | 29  | 28  | 27  | 26  | 25     | 24      | 23       | 22     | 21  | 20  | 19  | 18  | 17  | 16  |

|       |    |     | Counter 0 Compare Data |     |     |     |     |        |         |          |        |     |     |     |     |     |     |

|       | W  | D15 | D14                    | D13 | D12 | D11 | D10 | D9     | D8      | D7       | D6     | D5  | D4  | D3  | D2  | D1  | D0  |

| 10H   |    | D31 | D30                    | D29 | D28 | D27 | D26 | D25    | D24     | D23      | D22    | D21 | D20 | D19 | D18 | D17 | D16 |

| 1011  |    |     | Counter 0 Compare Data |     |     |     |     |        |         |          |        |     |     |     |     |     |     |

|       | R  | D15 | D14                    | D13 | D12 | D11 | D10 | D9     | D8      | D7       | D6     | D5  | D4  | D3  | D2  | D1  | D0  |

|       |    | D31 | D30                    | D29 | D28 | D27 | D26 | D25    | D24     | D23      | D22    | D21 | D20 | D19 | D18 | D17 | D16 |

|       |    |     | Counter 1 Compare Data |     |     |     |     |        |         |          |        |     |     |     |     |     |     |

|       | W  | D15 | D14                    | D13 | D12 | D11 | D10 | D9     | D8      | D7       | D6     | D5  | D4  | D3  | D2  | D1  | D0  |

| 14H   |    | D31 | D30                    | D29 | D28 | D27 | D26 | D25    | D24     | D23      | D22    | D21 | D20 | D19 | D18 | D17 | D16 |

| 1-7.1 | R  |     | Counter 1 Compare Data |     |     |     |     |        |         |          |        |     |     |     |     |     |     |

|       |    | D15 | D14                    | D13 | D12 | D11 | D10 | D9     | D8      | D7       | D6     | D5  | D4  | D3  | D2  | D1  | D0  |

|       |    | D31 | D30                    | D29 | D28 | D27 | D26 | D25    | D24     | D23      | D22    | D21 | D20 | D19 | D18 | D17 | D16 |

|       |    |     | Counter 2 Compare Data |     |     |     |     |        |         |          |        |     |     |     |     |     |     |

|       | W  | D15 | D14                    | D13 | D12 | D11 | D10 | D9     | D8      | D7       | D6     | D5  | D4  | D3  | D2  | D1  | D0  |

| 18H   |    | D31 | D30                    | D29 | D28 | D27 | D26 | D25    | D24     | D23      | D22    | D21 | D20 | D19 | D18 | D17 | D16 |

| 1011  |    |     | Counter 2 Compare Data |     |     |     |     |        |         |          |        |     |     |     |     |     |     |

|       | R  | D15 | D14                    | D13 | D12 | D11 | D10 | D9     | D8      | D7       | D6     | D5  | D4  | D3  | D2  | D1  | D0  |

|       |    | D31 | D30                    | D29 | D28 | D27 | D26 | D25    | D24     | D23      | D22    | D21 | D20 | D19 | D18 | D17 | D16 |

|       |    |     |                        |     |     |     |     | Coun   | ter 3 C | ompar    | e Data |     |     |     |     |     |     |

|       | W  | D15 | D14                    | D13 | D12 | D11 | D10 | D9     | D8      | D7       | D6     | D5  | D4  | D3  | D2  | D1  | D0  |

| 1CH   |    | D31 | D30                    | D29 | D28 | D27 | D26 | D25    | D24     | D23      | D22    | D21 | D20 | D19 | D18 | D17 | D16 |

| 1011  |    |     |                        |     |     |     |     | Coun   | ter 3 C | ompar    | e Data |     |     |     |     |     |     |

|       | R  | D15 | D14                    | D13 | D12 | D11 | D10 | D9     | D8      | D7       | D6     | D5  | D4  | D3  | D2  | D1  | D0  |

|       |    | D31 | D30                    | D29 | D28 | D27 | D26 | D25    | D24     | D23      | D22    | D21 | D20 | D19 | D18 | D17 | D16 |

Table C-1 PCI-1784 register format (Part 3)

| Base  |                  |          |                 |     |     |     |     | PCI-17 | '84 Re   | gister l | Forma | t   |     |     |     |     |     |

|-------|------------------|----------|-----------------|-----|-----|-----|-----|--------|----------|----------|-------|-----|-----|-----|-----|-----|-----|

|       | Address<br>+ HEX |          | 14              | 13  | 12  | 11  | 10  | 9      | 8        | 7        | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

| + HEX |                  | 31       | 30              | 29  | 28  | 27  | 26  | 25     | 24       | 23       | 22    | 21  | 20  | 19  | 18  | 17  | 16  |

|       |                  |          |                 |     |     |     |     | In     | terrup   | t Conti  | rol   |     |     |     |     |     |     |

|       | W                | DI3      | DI2             | DI1 | DI0 | IX3 | IX2 | IX1    | IX0      | UN3      | UN2   | UN1 | UN0 | OV3 | OV2 | OV1 | OV0 |

| 20H   |                  | ΙE       |                 |     | TM  |     |     |        |          | UC3      | UC2   | UC1 | UC0 | OC3 | OC2 | OC1 | OC0 |

|       |                  |          |                 |     |     |     |     | lr     | nterrup  | t Statu  | ıs    |     |     |     |     |     |     |

|       | R                | DI3      | DI2             | DI1 | DI0 | IX3 | IX2 | IX1    | IX0      | UN3      | UN2   | UN1 | UN0 | OV3 | OV2 | OV1 | OV0 |

|       |                  | IF       |                 |     | TM  |     |     |        |          | UC3      | UC2   | UC1 | UC0 | OC3 | OC2 | OC1 | OC0 |

|       |                  |          | Clock Control   |     |     |     |     |        |          |          |       |     |     |     |     |     |     |

|       | W                |          |                 |     |     |     |     |        |          |          |       |     |     |     |     | SC1 | SC0 |

| 24H   |                  |          |                 |     |     |     | TB2 | TB1    | TB0      | DV7      | DV6   | DV5 | DV4 | DV3 | DV2 | DV1 | DV0 |

| 2711  |                  |          | Clear Interrupt |     |     |     |     |        |          |          |       |     |     |     |     |     |     |

|       | R                |          |                 |     |     |     |     |        |          |          |       |     |     |     |     |     |     |

|       |                  |          |                 |     |     |     |     |        |          |          |       |     |     |     |     |     |     |

|       | W                |          | Software Latch  |     |     |     |     |        |          |          |       |     |     |     |     |     |     |

|       |                  |          |                 |     |     |     |     |        |          |          |       |     |     | SL3 | SL2 | SL1 | SL0 |

| 28H   |                  |          |                 |     |     |     |     |        |          |          |       |     |     |     |     |     |     |

|       |                  | Board ID |                 |     |     |     |     |        |          |          |       |     |     |     |     |     |     |

|       | R                |          |                 |     |     |     |     |        |          |          |       |     |     | BD3 | BD2 | BD1 | BD0 |

|       |                  |          |                 |     |     |     |     |        |          |          |       |     |     |     |     |     |     |

|       |                  |          | Reset Counter   |     |     |     |     |        |          |          |       |     |     |     |     |     |     |

|       | W                |          |                 |     |     |     |     |        |          |          |       |     |     | SR3 | SR2 | SR1 | SR0 |

| 2CH   |                  |          |                 |     |     |     |     |        |          |          |       |     |     |     |     |     |     |

|       |                  |          |                 |     | 1   |     |     |        | N        | /A       | T     |     |     |     |     | T   |     |

|       | R                |          |                 |     |     |     |     |        |          |          |       |     |     |     |     |     |     |

|       |                  |          |                 |     |     |     |     |        |          |          |       |     |     |     |     |     |     |

|       |                  | 1        |                 |     | 1   |     |     |        | Digital  | Outpu    | ıt    |     |     |     |     | ı   |     |

|       | W                |          |                 |     |     |     |     |        |          |          |       |     |     | DO3 | DO2 | DO1 | DO0 |

| 30H   |                  | DM3      | DM2             | DM1 | DM0 | LE3 | LE2 | LE1    | LE0      | UC3      | UC2   | UC1 | UC0 | OC3 | OC2 | OC1 | OC0 |

|       | _                | 1        |                 |     | 1   |     |     | Dig    | ital Inp | out/Out  |       |     |     |     |     | 1   |     |

|       | R                |          |                 |     |     |     |     |        |          | DI3      | DI2   | DI1 | DI0 | DO3 | DO2 | DO1 | DO0 |

|       |                  | DM3      | DM2             | DM1 | DM0 | LE3 | LE2 | LE1    | LE0      | UC3      | UC2   | UC1 | UC0 | OC3 | OC2 | OC1 | OC0 |

# C.3 Counter 0/1/2/3 mode — BASE+00/04/08/0CH

Table C-2 PCI-1784 Register for counter 0/1/2/3 mode

|        |       |     |     |     |     |    |    | . 0 | J     |         |    |    |    |    |    |    |    |

|--------|-------|-----|-----|-----|-----|----|----|-----|-------|---------|----|----|----|----|----|----|----|

| Base / | \ ddr | 15  | 14  | 13  | 12  | 11 | 10 | 9   | 8     | 7       | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

| Dase / | auui. | 31  | 30  | 29  | 28  | 27 | 26 | 25  | 24    | 23      | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|        |       |     |     |     |     |    |    | C   | ounte | r 0 Mod | de |    |    |    |    |    |    |

| 00H    | W     | DI3 | DI2 | DI1 | DI0 |    | TM | IX  | SW    | DF      | UL | OL | RF |    | M2 | M1 | MO |

|        |       |     |     |     |     |    |    |     |       |         |    |    |    |    |    |    |    |

|        |       |     |     |     |     |    |    | C   | ounte | r 1 Mod | de |    |    |    |    |    |    |

| 04H    | W     | DI3 | DI2 | DI1 | DI0 |    | TM | IX  | SW    | DF      | UL | OL | RF |    | M2 | M1 | MO |

|        |       |     |     |     |     |    |    |     |       |         |    |    |    |    |    |    |    |

|        |       |     |     |     |     |    |    | C   | ounte | r 2 Mod | de |    |    |    |    |    |    |

| 08H    | W     | DI3 | DI2 | DI1 | DI0 |    | TM | IX  | SW    | DF      | UL | OL | RF |    | M2 | M1 | MO |

|        |       |     |     |     |     |    |    |     |       |         |    |    |    |    |    |    |    |

|        |       |     |     |     |     |    |    | C   | ounte | r 3 Mod | de |    |    |    |    |    |    |

| 0CH    | W     | DI3 | DI2 | DI1 | DI0 |    | TM | IX  | SW    | DF      | UL | OL | RF |    | M2 | M1 | M0 |

|        |       |     |     |     |     |    |    |     |       |         |    |    |    |    |    |    |    |

| $M2 \sim M0$ | Counter  | input mode control                           |

|--------------|----------|----------------------------------------------|

|              | 000      | Disable                                      |

|              | 001      | Quadrature input x 1                         |

|              | 010      | Quadrature input x 2                         |

|              | 011      | Quadrature input x 4                         |

|              | 100      | 2 pulse input                                |

|              | 101      | 1 pulse input                                |

|              | 110      | N/A                                          |

|              | 111      | N/A                                          |

| RF           | Set coun | nter reset value                             |

|              | 0        | 80000000h                                    |

|              | 1        | 00000000h                                    |

| OL           | Counter  | overflow lock control                        |

|              | 0        | Counter continues counting (wraps over) when |

|              |          | counter overflow                             |

|              | 1        | Counter locked when counter overflow         |

| UL  | Cour  | nter underflow lock control                       |

|-----|-------|---------------------------------------------------|

|     | 0     | Counter continues counting (wraps over) when      |

|     |       | counter underflow                                 |

|     | 1     | Counter locked when counter underflow             |

| DF  | Digit | al Filter                                         |

|     | 0     | Quadrature input frequency without digital filter |

|     | 1     | Quadrature input frequency with digital filter    |

| SW  | Softv | vare latch counter data                           |

|     | 0     | Disable software latch                            |

|     | 1     | Enable software latch                             |

| IX  | Inde  | x latch counter data                              |

|     | 0     | Disable index latch                               |

|     | 1     | Enable index latch                                |

| TM  | Time  | r latch counter data                              |

|     | 0     | Disable timer latch                               |

|     | 1     | Enable timer latch                                |

| DIO | DIO I | atch counter data                                 |

|     | 0     | Disable DI0 latch                                 |

|     | 1     | Enable DI0 latch                                  |

| DI1 | DI1 l | atch counter data                                 |

|     | 0     | Disable DI1 latch                                 |

|     | 1     | Enable DI1 latch                                  |

| DI2 | DI2 l | atch counter data                                 |

|     | 0     | Disable DI2 latch                                 |

|     | 1     | Enable DI2 latch                                  |

| DI3 | DI3 l | atch counter data                                 |

|     | 0     | Disable DI3 latch                                 |

|     | 1     | Enable DI3 latch                                  |

# C.4 Counter 0/1/2/3 latch data — BASE+00/04/08/0CH

Table C-3 PCI-1784 Register for counter 0/1/2/3 latch data

| Base A | ۸ddr  | 15                   | 14  | 13  | 12  | 11  | 10  | 9   | 8      | 7     | 6    | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-------|----------------------|-----|-----|-----|-----|-----|-----|--------|-------|------|-----|-----|-----|-----|-----|-----|

| Dase / | -uui. | 31                   | 30  | 29  | 28  | 27  | 26  | 25  | 24     | 23    | 22   | 21  | 20  | 19  | 18  | 17  | 16  |

|        |       |                      |     |     |     |     |     | Cou | nter 0 | Latch | Data |     |     |     |     |     |     |

| 00H    | R     | D15                  | D14 | D13 | D12 | D11 | D10 | D9  | D8     | D7    | D6   | D5  | D4  | D3  | D2  | D1  | D0  |

|        |       | D31                  | D30 | D29 | D28 | D27 | D26 | D25 | D24    | D23   | D22  | D21 | D20 | D19 | D18 | D17 | D16 |

|        |       | Counter 1 Latch Data |     |     |     |     |     |     |        |       |      |     |     |     |     |     |     |

| 04H    | R     | D15                  | D14 | D13 | D12 | D11 | D10 | D9  | D8     | D7    | D6   | D5  | D4  | D3  | D2  | D1  | D0  |

|        |       | D31                  | D30 | D29 | D28 | D27 | D26 | D25 | D24    | D23   | D22  | D21 | D20 | D19 | D18 | D17 | D16 |

|        |       |                      |     |     |     |     |     | Cou | nter 2 | Latch | Data |     |     |     |     |     |     |

| 08H    | R     | D15                  | D14 | D13 | D12 | D11 | D10 | D9  | D8     | D7    | D6   | D5  | D4  | D3  | D2  | D1  | D0  |

|        |       | D31                  | D30 | D29 | D28 | D27 | D26 | D25 | D24    | D23   | D22  | D21 | D20 | D19 | D18 | D17 | D16 |

|        |       |                      |     |     |     |     |     | Cou | nter 3 | Latch | Data |     |     |     |     |     |     |

| 0CH    | R     | D15                  | D14 | D13 | D12 | D11 | D10 | D9  | D8     | D7    | D6   | D5  | D4  | D3  | D2  | D1  | D0  |

|        |       | D31                  | D30 | D29 | D28 | D27 | D26 | D25 | D24    | D23   | D22  | D21 | D20 | D19 | D18 | D17 | D16 |

D31 ~ D0 Counter latch data

# C.5 Counter 0/1/2/3 compare data — BASE+10/14/18/1CH

Table C-4 PCI-1784 Register for counter 0/1/2/3 compare data

|        |       |     |     |     |     |     | 6   |      |         |       |        |     |     |     |     |     |     |

|--------|-------|-----|-----|-----|-----|-----|-----|------|---------|-------|--------|-----|-----|-----|-----|-----|-----|

| Base   | Addr. | 15  | 14  | 13  | 12  | 11  | 10  | 9    | 8       | 7     | 6      | 5   | 4   | 3   | 2   | 1   | 0   |

| Duoc 2 | Addi. | 31  | 30  | 29  | 28  | 27  | 26  | 25   | 24      | 23    | 22     | 21  | 20  | 19  | 18  | 17  | 16  |

|        |       |     |     |     |     |     |     | Coun | ter 0 C | ompar | e Data |     |     |     |     |     |     |

|        | W     | D15 | D14 | D13 | D12 | D11 | D10 | D9   | D8      | D7    | D6     | D5  | D4  | D3  | D2  | D1  | D0  |

| 10H    |       | D31 | D30 | D29 | D28 | D27 | D26 | D25  | D24     | D23   | D22    | D21 | D20 | D19 | D18 | D17 | D16 |

| 1011   |       |     |     |     |     |     |     | Coun | ter 0 C | ompar | e Data |     |     |     |     |     |     |

|        | R     | D15 | D14 | D13 | D12 | D11 | D10 | D9   | D8      | D7    | D6     | D5  | D4  | D3  | D2  | D1  | D0  |

|        |       | D31 | D30 | D29 | D28 | D27 | D26 | D25  | D24     | D23   | D22    | D21 | D20 | D19 | D18 | D17 | D16 |

|        |       |     |     |     |     |     |     | Coun | ter 1 C | ompar | e Data |     |     |     |     |     |     |

|        | W     | D15 | D14 | D13 | D12 | D11 | D10 | D9   | D8      | D7    | D6     | D5  | D4  | D3  | D2  | D1  | D0  |

| 14H    |       | D31 | D30 | D29 | D28 | D27 | D26 | D25  | D24     | D23   | D22    | D21 | D20 | D19 | D18 | D17 | D16 |

| 1411   |       |     |     |     |     |     |     | Coun | ter 1 C | ompar | e Data |     |     |     |     |     |     |

|        | R     | D15 | D14 | D13 | D12 | D11 | D10 | D9   | D8      | D7    | D6     | D5  | D4  | D3  | D2  | D1  | D0  |

|        |       | D31 | D30 | D29 | D28 | D27 | D26 | D25  | D24     | D23   | D22    | D21 | D20 | D19 | D18 | D17 | D16 |

|        |       |     |     |     |     |     |     | Coun | ter 2 C | ompar | e Data |     |     |     |     |     |     |

|        | W     | D15 | D14 | D13 | D12 | D11 | D10 | D9   | D8      | D7    | D6     | D5  | D4  | D3  | D2  | D1  | D0  |

| 18H    |       | D31 | D30 | D29 | D28 | D27 | D26 | D25  | D24     | D23   | D22    | D21 | D20 | D19 | D18 | D17 | D16 |

| 1011   |       |     |     |     |     |     |     | Coun | ter 2 C | ompar | e Data |     |     |     |     |     |     |

|        | R     | D15 | D14 | D13 | D12 | D11 | D10 | D9   | D8      | D7    | D6     | D5  | D4  | D3  | D2  | D1  | D0  |

|        |       | D31 | D30 | D29 | D28 | D27 | D26 | D25  | D24     | D23   | D22    | D21 | D20 | D19 | D18 | D17 | D16 |

|        |       |     |     |     |     |     |     | Coun | ter 3 C | ompar | e Data |     |     |     |     |     |     |

|        | W     | D15 | D14 | D13 | D12 | D11 | D10 | D9   | D8      | D7    | D6     | D5  | D4  | D3  | D2  | D1  | D0  |

| 1CH    |       | D31 | D30 | D29 | D28 | D27 | D26 | D25  | D24     | D23   | D22    | D21 | D20 | D19 | D18 | D17 | D16 |

| 1011   |       |     |     |     |     |     |     | Coun | ter 3 C | ompar | e Data |     |     |     |     |     |     |

|        | R     | D15 | D14 | D13 | D12 | D11 | D10 | D9   | D8      | D7    | D6     | D5  | D4  | D3  | D2  | D1  | D0  |

|        |       | D31 | D30 | D29 | D28 | D27 | D26 | D25  | D24     | D23   | D22    | D21 | D20 | D19 | D18 | D17 | D16 |

D31 ~ D0 Counter compare data

## C.6 Interrupt control register — BASE+20H

OVn

Table C-5 PCI-1784 Register for interrupt control

| Base A | Δddr   | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8      | 7       | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|--------|-----|-----|-----|-----|-----|-----|-----|--------|---------|-----|-----|-----|-----|-----|-----|-----|

| Dase / | -tuui. | 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24     | 23      | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|        |        |     |     |     |     |     |     | In  | terrup | t contr | ol  |     |     |     |     |     |     |

| 20H    | W      | DI3 | DI2 | DI1 | DI0 | IX3 | IX2 | IX1 | IX0    | UN3     | UN2 | UN1 | UN0 | OV3 | OV2 | OV1 | OV0 |

|        |        | IE  |     |     | TM  |     |     |     |        | UC3     | UC2 | UC1 | UC0 | OC3 | OC2 | OC1 | OC0 |

Interrupt by overflow bit  $(n: 0 \sim 3)$

0 Disable 1 Enable UNn Interrupt by underflow bit  $(n: 0 \sim 3)$ 0 Disable 1 Enable IXnInterrupt by index status bit  $(n: 0 \sim 3)$ 0 Disable 1 Enable DInInterrupt by digital input bit  $(n: 0 \sim 3)$ 0 Disable 1 Enable Interrupt by counter over compare bit  $(n: 0 \sim 3)$ OCn0 Disable 1 Enable **UC**n Interrupt by counter under compare bit  $(n: 0 \sim 3)$ Disable 1 Enable TM

Interrupt by timer pulse bit

Disable Enable

IE Overall interrupt enable bit

> Disable 1 Enable

## C.7 Interrupt status register — BASE+20H

*Table C-6 PCI-1784 Register for interrupt status*

| Base / | ۸ddr   | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8       | 7        | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|--------|-----|-----|-----|-----|-----|-----|-----|---------|----------|-----|-----|-----|-----|-----|-----|-----|

| Dase / | -tuui. | 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24      | 23       | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|        |        |     |     |     |     |     |     | li  | nterrup | ot statu | IS  |     |     |     |     |     |     |

| 20H    | R      | DI3 | DI2 | DI1 | DI0 | IX3 | IX2 | IX1 | IX0     | UN3      | UN2 | UN1 | UN0 | OV3 | OV2 | OV1 | OV0 |

|        |        | IF  |     |     | TM  |     |     |     |         | UC3      | UC2 | UC1 | UC0 | OC3 | OC2 | OC1 | OC0 |

OVnCounter overflow interrupt flag ( $n: 0 \sim 3$ ) Disable 1 Enable UNn Counter underflow interrupt flag  $(n: 0 \sim 3)$ 0 Disable 1 Enable IXnIndex input interrupt flag  $(n: 0 \sim 3)$ 0 Disable 1 Enable Digital input interrupt flag  $(n: 0 \sim 3)$ DIn0 Disable 1 Enable Counter over compare interrupt by flag  $(n: 0 \sim 3)$ OCn0 Disable 1 Enable **UC**n Counter under compare interrupt flag  $(n: 0 \sim 3)$ Disable 1 Enable TMTimer pulse interrupt flag 0 Disable

1 Enable

IF Overall interrupt enable flag

0 Disable1 Enable

# C.8 Clear Interrupt — BASE+24H

Table C-7 PCI-1784 Register for clock control

| Base A | ۸ddr  | 15 | 14 | 13 | 12 | 11 | 10  | 9   | 8     | 7      | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-------|----|----|----|----|----|-----|-----|-------|--------|-----|-----|-----|-----|-----|-----|-----|

| Dase A | -uui. | 31 | 30 | 29 | 28 | 27 | 26  | 25  | 24    | 23     | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|        |       |    |    |    |    |    |     |     | Clock | Contro | ol  |     |     |     |     |     |     |

| 24H    | W     |    |    |    |    |    |     |     |       |        |     |     |     |     |     | SC1 | SC0 |

|        |       |    |    |    |    |    | TB2 | TB1 | TB0   | DV7    | DV6 | DV5 | DV4 | DV3 | DV2 | DV1 | DV0 |

| Samplin  | ng clock select                                                                       |

|----------|---------------------------------------------------------------------------------------|

| 00       | 8 MHz sampling clock                                                                  |

| 01       | 4 MHz sampling clock                                                                  |

| 10       | 2 MHz sampling clock                                                                  |

| 11       | 1 MHz sampling clock                                                                  |

| Timer d  | ivider control                                                                        |

| Timer ti | me base select                                                                        |

| 000      | 50 KHz time base                                                                      |

| 001      | 5 KHz time base                                                                       |

| 010      | 500 Hz time base                                                                      |

| 011      | 50 Hz time base                                                                       |

| 100      | 5 Hz time base                                                                        |

| 101      | N/A                                                                                   |

| 110      | N/A                                                                                   |

| 111      | N/A                                                                                   |

|          | 00<br>01<br>10<br>11<br>Timer d<br>Timer ti<br>000<br>001<br>010<br>011<br>100<br>101 |

# C.9 Clear Interrupt — BASE+24H

Read this register to clear the interrupt.

Table C-8 PCI-1784 Register for clear interrupt

| Base / | ۸ddr  | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8        | 7       | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|--------|-------|----|----|----|----|----|----|----|----------|---------|----|----|----|----|----|----|----|

| Dase / | -uui. | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24       | 23      | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|        |       |    |    |    |    |    |    | (  | Clear II | nterrup | ot |    |    |    |    |    |    |

| 24H    | R     |    |    |    |    |    |    |    |          |         |    |    |    |    |    |    |    |

|        |       |    |    |    |    |    |    |    |          |         |    |    |    |    |    |    |    |

## C.10 Software latch — BASE+28H

Table C-9 PCI-1784 Register for software latch

| Base / | ۸ddr  | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8      | 7      | 6  | 5  | 4  | 3   | 2   | 1   | 0   |

|--------|-------|----|----|----|----|----|----|----|--------|--------|----|----|----|-----|-----|-----|-----|

| Dase / | -uui. | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24     | 23     | 22 | 21 | 20 | 19  | 18  | 17  | 16  |

|        |       |    |    |    |    |    |    | 5  | Softwa | e Lato | :h |    |    |     |     |     |     |

| 28H    | W     |    |    |    |    |    |    |    |        |        |    |    |    | SL3 | SL2 | SL1 | SL0 |

|        |       |    |    |    |    |    |    |    |        |        |    |    |    |     |     |     |     |

SL*n* Software latch command  $(n: 0 \sim 3)$

0 N/A

1 Latch counter to latch register

### C.11 Board ID — BASE+28H

The PCI-1784 offers Board ID register BASE+28H. With correct Board ID settings, user can easily identify and access each card during hardware configuration and software programming.

Table C-10 PCI-1784 Board ID data

| Base / | ۸ddr   | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8   | 7     | 6  | 5  | 4  | 3   | 2   | 1   | 0   |

|--------|--------|----|----|----|----|----|----|----|-----|-------|----|----|----|-----|-----|-----|-----|

| Dase / | -tuui. | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24  | 23    | 22 | 21 | 20 | 19  | 18  | 17  | 16  |

|        |        |    |    |    |    |    |    |    | Boa | rd ID |    |    |    |     |     |     |     |

| 28H    | R      | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0     | 0  | 0  | 0  | BD3 | BD2 | BD1 | BD0 |

|        |        | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0     | 0  | 0  | 0  | 0   | 0   | 0   | 0   |

### BD3 ~ DB0 Board ID

BD0 LSB of the Board IDBD3 MSB of the Board ID

| BD3 | BD2 | BD1 | BD0 | Board ID |

|-----|-----|-----|-----|----------|

| 1   | 1   | 1   | 1   | 15       |

| 1   | 1   | 1   | 0   | 14       |

| 1   | 1   | 0   | 1   | 13       |

| 1   | 1   | 0   | 0   | 12       |

| 1   | 0   | 1   | 1   | 11       |

| 1   | 0   | 1   | 0   | 10       |

| 1   | 0   | 0   | 1   | 9        |

| 1   | 0   | 0   | 0   | 8        |

| 0   | 1   | 1   | 1   | 7        |

| 0   | 1   | 1   | 0   | 6        |

| 0   | 1   | 0   | 1   | 5        |

| 0   | 1   | 0   | 0   | 4        |

| 0   | 0   | 1   | 1   | 3        |

| 0   | 0   | 1   | 0   | 2        |

| 0   | 0   | 0   | 1   | 1        |

| 0   | 0   | 0   | 0   | 0        |

## C.12 Reset counter — BASE+2CH

Table C-11 PCI-1784 Register for reset counter

| Base / | ۸ddr  | 15 | 14            | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3   | 2   | 1   | 0   |

|--------|-------|----|---------------|----|----|----|----|----|----|----|----|----|----|-----|-----|-----|-----|

| Dase / | -uui. | 31 | 30            | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19  | 18  | 17  | 16  |

|        |       |    | Reset Counter |    |    |    |    |    |    |    |    |    |    |     |     |     |     |

| 2CH    | W     |    |               |    |    |    |    |    |    |    |    |    |    | SR3 | SR2 | SR1 | SR0 |

|        |       |    |               |    |    |    |    |    |    |    |    |    |    |     |     |     |     |

**SR***n* Reset counter command  $(n: 0 \sim 3)$

0 N/A

1 Reset counter to default value

## C.13 Digital output — BASE+30H

Table C-12 PCI-1784 Register for digital output

| Base /     | ۸ddr | 15  | 14             | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------------|------|-----|----------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| base Auui. |      | 31  | 30             | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|            |      |     | Digital Output |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| 30H        | W    |     |                |     |     |     |     |     |     |     |     |     |     | DO3 | DO2 | DO1 | DO0 |

|            |      | DM3 | DM2            | DM1 | DM0 | LE3 | LE2 | LE1 | LE0 | UC3 | UC2 | UC1 | UC0 | OC3 | OC2 | OC1 | OC0 |

DO3 ~ DO0

Digital output data

OCn

Digital output by over compare register  $(n: 0 \sim 3)$ UCn

Digital output by under compare register  $(n: 0 \sim 3)$ LEn

Digital output level control  $(n: 0 \sim 3)$ 0

Pulse with counter clock

1

Level with clear interrupt

DMn

Digital output mode control  $(n: 0 \sim 3)$

NormalIndicated

## C.14 Digital input/output — BASE+30H

Table C-13 PCI-1784 Register for digital input/output

| Base /     | ۸ddr | 15  | 14                   | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------------|------|-----|----------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| base Addi. | aui. | 31  | 30                   | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|            |      |     | Digital Input/Output |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| 30H        | R    |     |                      |     |     |     |     |     |     | DI3 | DI2 | DI1 | DI0 | DO3 | DO2 | DO1 | DO0 |

|            |      | DM3 | DM2                  | DM1 | DM0 | LE3 | LE2 | LE1 | LE0 | UC3 | UC2 | UC1 | UC0 | OC3 | OC2 | OC1 | OC0 |

**DO3** ~ **DO0** Digital output data **DI3** ~ **DI0** Digital input data Digital output by over compare register  $(n: 0 \sim 3)$ OCn**UC**n Digital output by under compare register  $(n: 0 \sim 3)$ Digital output level control (n: 0 ~ 3) LEn 0 Pulse with counter clock Level with clear interrupt DMnDigital output mode control (n: 0 ~ 3) 0 Normal 1 Indicated

## **Appendix D. Operation**

## D.1 Quadrature encoder introduction

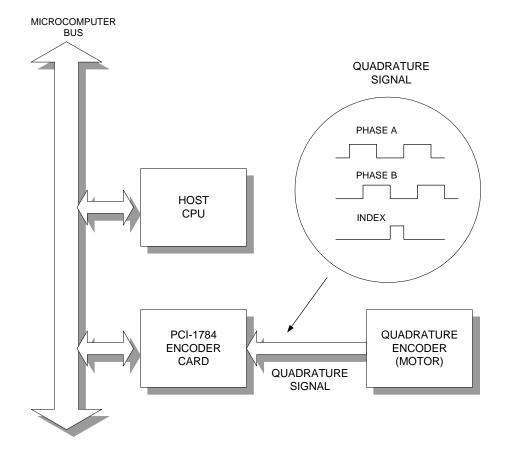

In typical closed-loop control systems, also know as servo system, the encoder interface senses motor position and sends a position signal to the controller. The diagram below shows a typical servo system.

The encoder generates pulses which indicate the shaft position. The encoder output includes two signals, commonly called channel A and channel B, which generate N pulses revolution. The two signals are shifted by a quarter of a cycle, as shown below. The shift between the two signals enables the controller to determine the direction of rotation, depending on whether channel A leads channel B or vice versa.

#### Single-ended vs. differential input

Most encoders produce square wave signals with TTL levels. Industrial systems often use encoder with differential signals, i.e. channel A and B and their complements. Differential signals can reduce sensitivity to noise and allow longer transmission distances. Encoders may also produce a third signal once per revolution know as the index or marker. The encoder interface can use the index signal to reset the counter, allowing you to monitor the position within the current revolution.

### D.2 Counter modes

The following table shows the maximum input rate for each input mode and system clock rate. Values are given for each system clock frequency.

| Mode                  |       | Maximum | input rate |         |

|-----------------------|-------|---------|------------|---------|

| -                     | 8MHz  | 4MHz    | 2MHz       | 1MHz    |

| Quadrature x1, x2, x4 | 2 MHz | 1 MHz   | 500 KHz    | 250 KHz |

| 2-pulse               | 8 MHz | 4 MHz   | 2 MHz      | 1 MHz   |

| Pulse/direction       | 8 MHz | 4 MHz   | 2 MHz      | 1 MHz   |

Counter modes are as follows:

### Quadrature input counter mode

Quadrature input consists of two square wave inputs (A and B)which are 90° out of phase. The PCI-1784 counts square wave transitions and determines the direction by comparing whether channel A is leading channel B or vice versa.

There are three different counting methods in quadrature input mode:

- **x1** The counter will increment (or decrement) the counter whenever a rising edge occurs on input channel A.

- **x2** The counter will increment (or decrement) whenever a rising or falling edge occurs on input channel A.

- **x4** The counter will increment (or decrement) whenever a rising or falling edge occurs on input channel A or B.

#### 2-pulse mode

In 2-pulse mode the PCI-1784 uses two input pulses as counting sources: one for clockwise (CW) and one for counterclockwise (CCW) counting. The counter will increment whenever a rising edge occurs on channel A. It will decrement whenever a rising edge occurs on channel B.

#### pulse/direction mode

In pulse/direction mode the PCI-1784 uses one input line (A) for pulse input and one line (B) for direction. If channel B is high (1), the counter will decrement whenever a rising edge occurs in channel A. If channel B is low (0), the counter will increment whenever a rising edge occurs on channel A.

#### Disabled mode

PCI-1784 will not accept input, but you can access all its registers.

You select the mode by programming the card's registers: BASE+00H for CH0, BASE+04H for CH1, BASE+08H for CH2 and BASE+0CH for CH3. See Appendix C for more information.

## D.3 Digital noise filter

Noise immunity is the most important requirement for reliable encoder interface operation. The PCI-1784 conditions the input signal with a four stage digital filter. This filter reduces glitches (digital noise) or spikes by sampling by sampling the input at 1, 2, 4 or 8MHz. The filter output waveforms change only when an input has the same value for four consecutive sampling edges. The filter thus rejects noise or pulses shorter than four sampling clock periods. You can optimize noise immunity by selecting the lowest sampling frequency that compatible with the highest input rate you expect.

The PCI-1784 accepts up to 2 MHz quadrature frequency at 8 MHz filter sampling speed. At 2 MHz sampling speed it can still accept up

to 500 KHz quadrature input frequency.

A 3600 rpm motor with 2000 ppr encoder will nave a maximum quadrature frequency of  $3600\times2000\div60=120$  KHz. In the above example the 2 MHz sampling clock will have the noise immunity and will meet the required input frequency.

The following table shows the maximum noise pulse width that the filter will reject for each system clock frequency:

| Clock frequency | Maximum width |  |

|-----------------|---------------|--|